在工業(yè)制造、建筑裝飾及家居生活中,不銹鋼材料以其卓越的耐腐蝕性、高強度及美觀的金屬光澤,成為不可或缺的重要材料。鑫城盟金屬作為專業(yè)的金屬材料供應商,致力于為客戶提供高品質的不銹鋼產品。本文將結合高清大圖,深入解析不銹鋼材料架及其相關金屬材料的特性與應用。

一、不銹鋼材料架:結構、功能與高清視覺呈現

不銹鋼材料架是倉儲、車間及零售環(huán)境中常見的存儲設備,主要用于分類、存放各類金屬型材、板材及零部件。鑫城盟金屬提供的不銹鋼材料架,通常采用304或316等優(yōu)質不銹鋼制成,確保在潮濕或酸堿環(huán)境下仍能保持結構穩(wěn)定、不易生銹。

通過高清大圖,我們可以清晰觀察到材料架的細節(jié)設計:

- 結構穩(wěn)固性:架體采用焊接或螺栓連接,承重能力強,層板可調節(jié),適應不同尺寸材料的存放。

- 表面處理:表面經過拋光或拉絲處理,呈現細膩的金屬紋理,不僅美觀,還易于清潔維護。

- 應用場景:高清圖片展示了材料架在工廠車間、建材市場等環(huán)境中的實際使用情況,凸顯其耐用性與實用性。

二、不銹鋼材料種類與特性高清解析

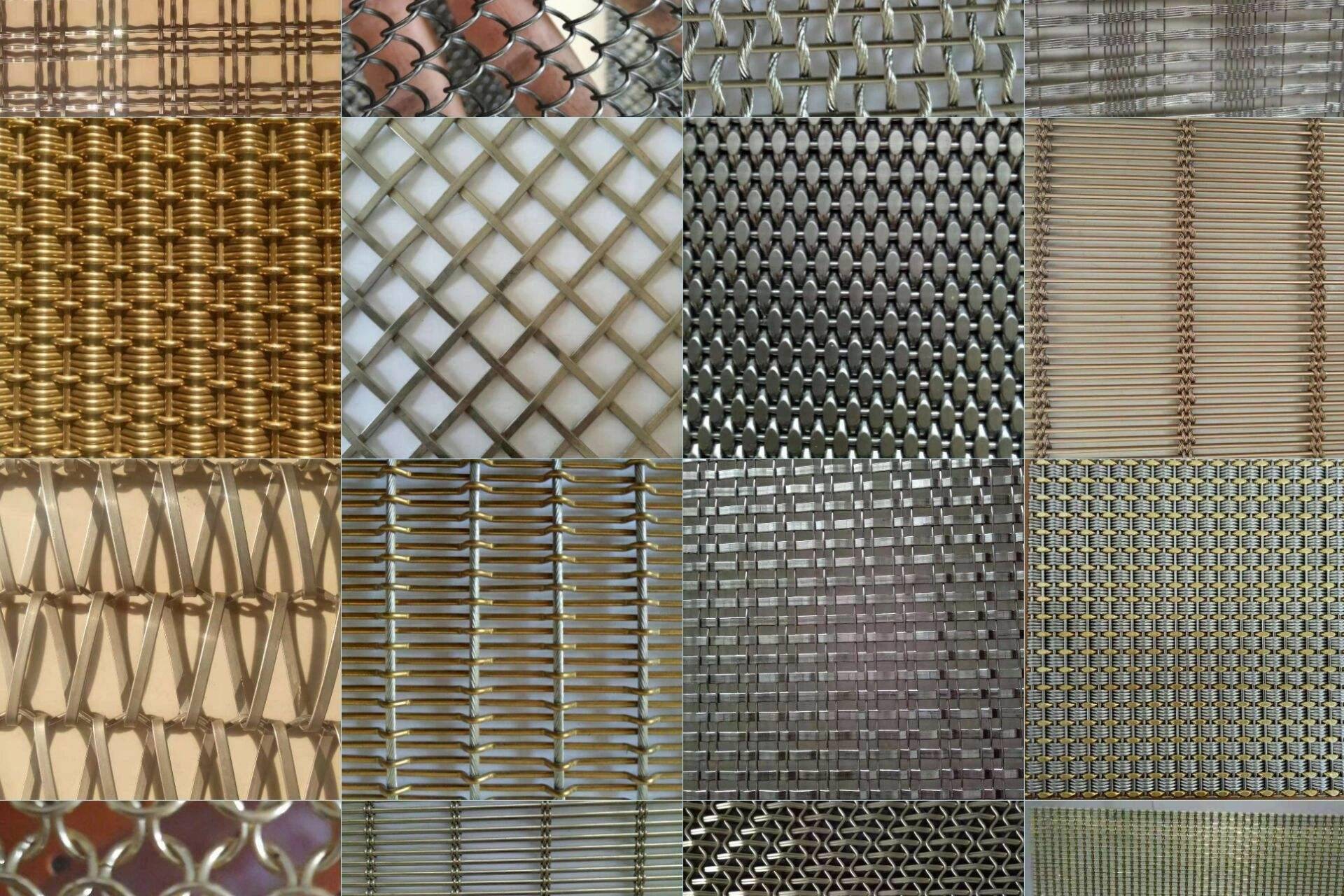

鑫城盟金屬供應的不銹鋼材料涵蓋多種類型,高清大圖能幫助用戶直觀區(qū)分其外觀與質感:

- 奧氏體不銹鋼(如304、316):高清特寫顯示其表面光滑、延展性好,常用于食品設備、醫(yī)療器械及戶外建筑。

- 馬氏體不銹鋼(如410、420):圖片呈現較高硬度與磁性,適用于刀具、機械零件等需要耐磨的場景。

- 鐵素體不銹鋼(如430):高清圖中可見其磁性較強、耐腐蝕性適中,多用于家電裝飾及汽車排氣管。

通過對比高清圖像,用戶可輕松識別不同材料的色澤差異(如304的銀亮色與316的灰白色調),以及表面處理效果(如鏡面、磨砂等)。

三、金屬材料的綜合應用與選購建議

不銹鋼作為金屬材料的代表,其性能優(yōu)勢在高清大圖中得到充分體現:無銹蝕斑點、均勻的金屬光澤、無變形結構等。鑫城盟金屬建議用戶在選購時:

- 根據環(huán)境選擇:潮濕或沿海地區(qū)宜選用316不銹鋼,一般室內環(huán)境可使用304不銹鋼。

- 關注厚度與強度:高清圖片可輔助判斷材料厚度,結合承重需求選擇合適規(guī)格。

- 注重視覺與實用平衡:裝飾用途需注重表面美觀度,工業(yè)用途則應優(yōu)先考慮結構強度。

不銹鋼材料架與金屬材料的高清展示,不僅提供了視覺參考,更幫助用戶深入理解材料特性。鑫城盟金屬通過優(yōu)質產品與清晰圖像,助力客戶做出明智選擇。隨著材料技術發(fā)展,不銹鋼將在更多領域展現其金屬魅力,成為可靠與美學的雙重保障。